| version: | Э. |

|----------|----|

|          |    |

|          |    |

Total Page: 26

# **CUSTOMER APPROVAL SHEET**

| Company                |                                  |

|------------------------|----------------------------------|

| Name                   |                                  |

| MODEL                  | H381DLN01.0                      |

| CUSTOMER               | Title :                          |

| APPROVED               | Name :                           |

| APPROVAL FOR SPECIFICA | ATIONS ONLY (Spec. Ver)          |

| APPROVAL FOR SPECIFICA | ATIONS AND ES SAMPLE (Spec. Ver) |

| APPROVAL FOR SPECIFICA | ATIONS AND CS SAMPLE (Spec. Ver) |

| CUSTOMER REMARK:       |                                  |

1 Li-Hsin Rd. 2. Science-Based Industrial Park Hsinchu 300, Taiwan, R.O.C.

| Doc. version : | 5.0        |

|----------------|------------|

| Total pages:   | 26         |

| Date :         | 2016/03/11 |

# Product Specification 3.81" COLOR AMOLED MODULE

## MODEL NAME: H381DLN01.0

Trial-run sample P/N: 95.03H70.000

MP product P/N: (TBD)

- >Preliminary Specification

- < >Final Specification

Note: The content of this specification is subject to change.

© 2015 AU Optronics All Rights Reserved, Do Not Copy.

## **Record of Revision**

| Version | Revise Date | Page     | Content                                          |  |  |  |

|---------|-------------|----------|--------------------------------------------------|--|--|--|

| 1.0     | 2015-11-09  | 1~26     | First Draft                                      |  |  |  |

|         |             | 9        | Add Power IC pin note.                           |  |  |  |

| 2.0     | 2015-11-09  | 17       | Initial Setting Modify, change OVSS setting, RAM |  |  |  |

|         |             | 17       | bypass.                                          |  |  |  |

| 3.0     | 2016-01-04  | 9        | Recommend Power IC description.                  |  |  |  |

| 4.0     | 2016-01-18  | 4        | Physical spec. Outline Dimension (w IQE)         |  |  |  |

| 4.0     | 2010-01-16  | 26       | Module outline (w IQE)                           |  |  |  |

|         |             | 5~6      | Pin Assignment                                   |  |  |  |

|         |             | 9        | Recommend DC/DC Power IC Application Circuit     |  |  |  |

| 5.0     | 2016 02 11  | 11       | Scan Direction                                   |  |  |  |

| 5.0     | 2016-03-11  | 16       | Power on/off sequence                            |  |  |  |

|         |             | 17       | Initial setting                                  |  |  |  |

|         |             | 26       | Module Outline                                   |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         | 1           |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         | )           |          |                                                  |  |  |  |

|         |             |          |                                                  |  |  |  |

|         |             | <u> </u> |                                                  |  |  |  |

## **Contents**

| м. | (30) | ıcıai əpecilicativii                         | <del>- 4</del> |

|----|------|----------------------------------------------|----------------|

|    | 1.   | Physical Specifications                      |                |

|    | 2.   | Pin Assignment                               |                |

|    | _,   | -                                            |                |

|    | 3.   | Absolute Maximum Ratings                     | 6              |

| В. | DC   | Characteristics                              | 7              |

|    | 1.   | Typical Operating Conditions                 | 7              |

|    | 2.   | Display Current Consumption                  | 8              |

|    | 3.   | Recommend DC/DC Power IC Application Circuit | 9              |

| C. | AC   | Characteristics                              | 10             |

|    | 1.   | Display Video Timing                         | 10             |

|    | 2.   | Scan Direction                               | 11             |

|    | 3.   | MIPI Interface Characteristics               |                |

|    | 4.   | Display RESET Timing Characteristics         | 14             |

|    | 5.   | Recommended Operating Sequence               | 15             |

| D. |      | ical Specification                           | 18             |

| E. | Reli | ability Test Items                           | 22             |

| F. | Pre  | cautions                                     | <b>2</b> 4     |

| G. | Pac  | king Information                             | 25             |

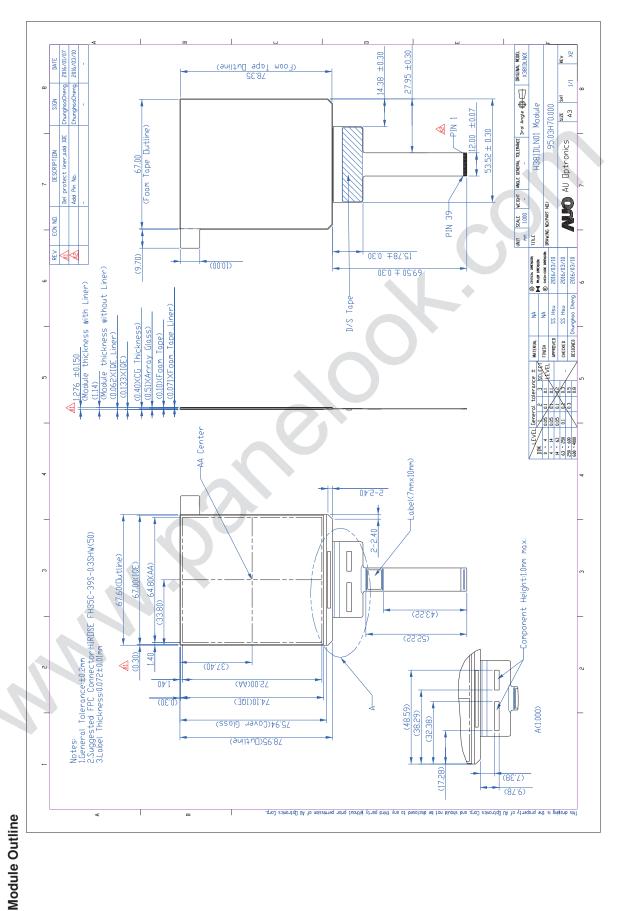

| н  | Out  | line Dimension                               | 26             |

## A. General Specification

## 1. Physical Specifications

| NO | Item                     | unit | Specification                   | Remark      |

|----|--------------------------|------|---------------------------------|-------------|

| 1  | Screen Size              | inch | 3.81"                           | Diagonal    |

| 2  | Display Resolution       |      | 1080(H) X 1200(V)               |             |

| 3  | <b>Outline Dimension</b> | mm   | 67.60 (H) x 78.95 (V) x 1.14(T) |             |

| 4  | Active Area              | mm   | 64.80 (H) x 72.0 (V)            |             |

| 5  | Pixel Pitch              | um   | 60                              |             |

| 6  | Color Configuration      |      | R, G, B                         |             |

| 7  | Color Depth              |      | 16.7M                           | 8-bit x RGB |

| 8  | NTSC Ratio               | %    | 100                             | CIE 1931    |

| 9  | Display Mode             |      | AMOLED                          |             |

| 10 | Interface                |      | MIPI DSI - Video Mode           |             |

| 11 | Driver IC                |      | Raydium                         | RM69071     |

#### **Pin Assignment** 2.

AMOLED Main FPC Pin assignment

| #  | Pin_name | I/O/P | Description                                                       |

|----|----------|-------|-------------------------------------------------------------------|

| 1  | OVSS     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 2  | OVSS     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 3  | OVSS     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 4  | OVDD     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 5  | OVDD     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 6  | OVDD     | Р     | OLED Power ( Power IC need to follow AUO's suggestion )           |

| 7  | GND      | G     | Ground                                                            |

| 8  | D2N      | I     | MIPI DSI data                                                     |

| 9  | D2P      | I     | MIPI DSI data                                                     |

| 10 | GND      | G     | Ground                                                            |

| 11 | D0N      | I/O   | MIPI DSI data                                                     |

| 12 | D0P      | I/O   | MIPI DSI data                                                     |

| 13 | GND      | G     | Ground                                                            |

| 14 | CLKN     | I     | MIPI DSI clock                                                    |

| 15 | CLKP     | I     | MIPI DSI clock                                                    |

| 16 | GND      | G     | Ground                                                            |

| 17 | D1N      | I     | MIPI DSI data                                                     |

| 18 | D1P      | I     | MIPI DSI data                                                     |

| 19 | GND      | G     | Ground                                                            |

| 20 | D3N      | I     | MIPI DSI data                                                     |

| 21 | D3P      | I     | MIPI DSI data                                                     |

| 22 | GND      | G     | Ground                                                            |

| 23 | IOVCC    | Р     | Display Driver Digital Power                                      |

| 24 | IOVCC    | Р     | Display Driver Digital Power                                      |

| 25 | VCI      | P     | Display Driver Analog Power                                       |

| 26 | VCI      | Р     | Display Driver Analog Power                                       |

| 07 | DECY     |       | This signal will reset the device and must be applied to properly |

| 27 | RESX     | l     | initialize the chip. Signal is active low.                        |

| 20 | SWIRE    | 0     | DC/DC power IC control signal                                     |

| 28 | SWINE    | 0     | ( Power IC need to follow AUO's suggestion )                      |

| 29 | AVDD_EN  | 0     | DC/DC power IC control signal                                     |

| 29 | WADD_EIN | 0     | ( Power IC need to follow AUO's suggestion )                      |

| 30 | MTP      | Р     | Leave this pin OPEN                                               |

| 31 | GND      | G     | Ground                                                            |

| 32 | AVDD     | Р     | Display Driver IC Source Analog Power                             |

| 02 | AVDD     | '     | ( Power IC need to follow AUO's suggestion )                      |

| 33 | AVDD     | Р     | Display Driver IC Source Analog Power                             |

| 33 | AVDD     | '     | ( Power IC need to follow AUO's suggestion )                      |

| 34 | OVDD | Р | OLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

|----|------|---|---------------------------------------------------------|--|--|

| 35 | OVDD | Р | OLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

| 36 | OVDD | Р | OLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

| 37 | OVSS | Р | DLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

| 38 | OVSS | Р | OLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

| 39 | OVSS | Р | OLED Power ( Power IC need to follow AUO's suggestion ) |  |  |

Recommended connector: Hirose FH35C-39S-0.3SHW (50)

## 3. Absolute Maximum Ratings

| Item                          | Symbol | Min. | Max.  | Unit | Remark |

|-------------------------------|--------|------|-------|------|--------|

| OLED Power supply             | OVDD   | -    | 4.6   | V    |        |

| OLED Power supply             | OVSS   | -    | -2.9  | V    |        |

| Driver IC Source power supply | AVDD   | -    | 5.8   | V    |        |

| Digital Power supply          | IOVCC  | -0.3 | +1.95 | V    |        |

| Analog Power supply           | VCI    | -0.3 | +3.2  | V    |        |

Note: If the module exceeds the absolute maximum ratings, it may be damaged permanently. Also, if the module operates with the absolute maximum ratings for a long time, the reliability may drop.

## **B. DC Characteristics**

## 1. Typical Operating Conditions

| Item                     |         | Symbol          | Min.       | Тур. | Max.       | Unit | Remark |

|--------------------------|---------|-----------------|------------|------|------------|------|--------|

| OLED Power supply        |         | OVDD            | -          | 4.6  | -          | V    |        |

| OLED Power supply        |         | ovss            | -          | -2.9 | -          | V    |        |

| Driver IC Source power s | upply   | AVDD            | -          | 5.8  | -          | V    |        |

| Digital Power supply     |         | IOVCC           | 1.65       | 1.80 | 1.95       | V    |        |

| Analog Power supply      |         | VCI             | 2.8        | 3.0  | 3.2        | V    |        |

| Input Cianal Valtage     | H Level | V <sub>IH</sub> | 0.8* IOVCC | 1    | IOVCC      | V    | RESX   |

| Input Signal Voltage     | L Level | V <sub>IL</sub> | 0          | -    | 0.2* IOVCC | V    | nesa   |

Note 1: The operation is guaranteed under the recommended operating conditions only. The operation is not guaranteed if a quick voltage change occurs during the operation. To prevent the noise, a bypass capacitor must be inserted into the line closed to the power pin.

## **Display Current Consumption**

| Mode                  | Symbol            | Condition    | Min. | Тур. | Max. | Unit | Remark      |

|-----------------------|-------------------|--------------|------|------|------|------|-------------|

|                       | I <sub>AVDD</sub> |              | -    | 15   | 30   | mA   |             |

|                       | IVCI              |              | -    | 3    | 3    | mA   | Note 1      |

| Normal                | lovcc             | AVDD = 5.8V  | -    | 38   | 40   | mA   |             |

|                       | lovdd             | VCI = 3V     | -    | -    | 16   | mA   | Note 2      |

|                       | lovss             | IOVCC = 1.8V | -    | -    | 16   | mA   | Note 2      |

|                       | lavdd             | OVDD = 4.6V  | -    | -    | 1    | uA   |             |

| Doon Standby          | IVCI              | OVSS = -2.9V | -    | -    | 3    | mA   |             |

| Deep Standby (DSTB=1) | lovcc             | 25℃          | -    | -    | 30   | uA   | Display Off |

| (DSTB=1)              | lovdd             |              | -    | -    | 0    | uA   |             |

|                       | lovss             |              | -    | -    | 0    | uA   |             |

Note 2: 100 nits White.

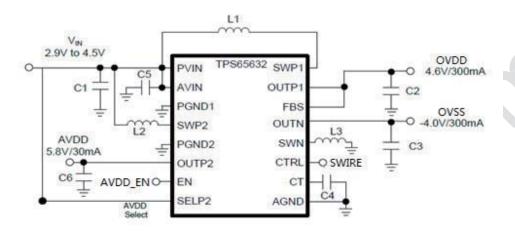

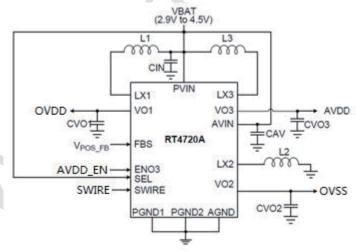

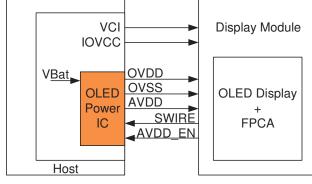

## 3. Recommend DC/DC Power IC Application Circuit

## **Power IC**

| Vendor  | Model        |

|---------|--------------|

| TI      | TPS65632RTER |

| Richtek | RT4720A      |

Bill of Materials

|        | Value    | Part Number       | Manufacturer |

|--------|----------|-------------------|--------------|

| C1     | 3 x 10μF | GRM21BR71A106KE51 | Murata       |

| C2, C6 | 10μF     | GRM21BR71A106KE51 | Murata       |

| C3     | 2 x 10μF | GRM21BR71A106KE51 | Murata       |

| C4, C5 | 100nF    | GRM21BR71E104KA01 | Murata       |

| L1, L3 | 4.7μΗ    | XFL4020-4R7ML     | CoilCraft    |

| L2     | 10μΗ     | MMPP252012-100N   | Coil Master  |

Bill of Materials

| Component      | Value  | Part Number       | Manufacture |

|----------------|--------|-------------------|-------------|

| CIN            | 10μFx3 | GRM21BR71A106KE51 | Murata      |

| CVO1,CVO2,CVO3 | 10μF   | GRM21BR71A106KE51 | Murata      |

| L1,L2          | 4.7μΗ  | DFE252012C-4R7N   | токо        |

| L3             | 10μΗ   | DFE252012C-100M   | токо        |

AUO don't suggest use other power IC instead of TPS65632RTER/ RT4720A, since they don't be qualified by AUO.

## C. AC Characteristics

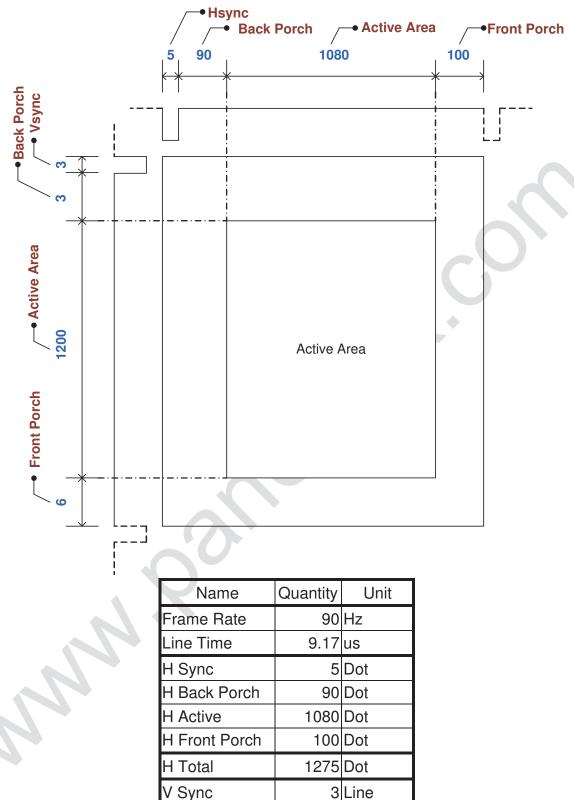

## 1. **Display Video Timing**

3 Line

6 Line

1200 Line

1212 Line

V Back Porch

V Front Porch

V Active

Total

#### **MIPI Interface Characteristics** 3.

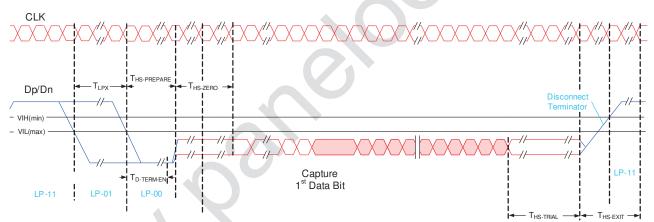

## **HS Data Transmission Burst**

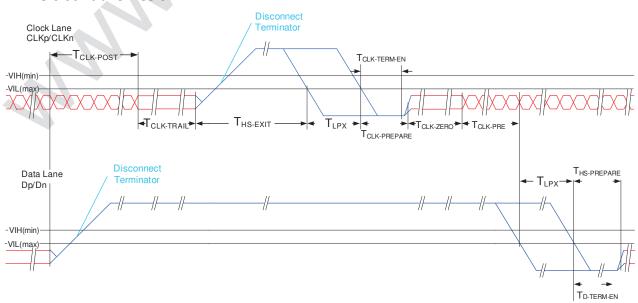

#### **HS clock transmission**

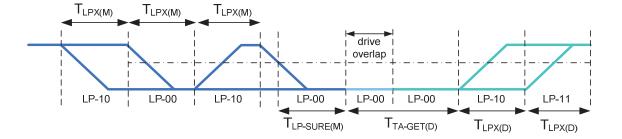

#### **Turnaround Procedure**

## **Timing Parameters**

| Timing Parameters        |                                                             |                            |     |         |      |

|--------------------------|-------------------------------------------------------------|----------------------------|-----|---------|------|

| Symbol                   | Description                                                 | Min                        | Тур | Max     | Unit |

| T <sub>CLK-POST</sub>    | Time that the transmitter continues to send                 | 60ns + 52*UI               |     |         | ns   |

|                          | HS clock after the last associated Data Lane                |                            |     |         |      |

|                          | has transitioned to LP Mode. Interval is                    |                            | 6   |         |      |

|                          | defined as the period from the end of $T_{HS-}$             | 4                          |     |         |      |

|                          | TRAIL to the beginning of T <sub>CLK-TRAIL</sub> .          |                            | •   |         |      |

| T <sub>CLK-TRAIL</sub>   | Time that the transmitter drives the HS-0                   | 60                         |     |         | ns   |

|                          | state after the last payload clock bit of a HS              |                            |     |         |      |

|                          | transmission burst.                                         |                            |     |         |      |

| $T_{HS-EXIT}$            | Time that the transmitter drives LP-11                      | 300                        |     |         | ns   |

|                          | following a HS burst.                                       |                            |     |         |      |

| T <sub>CLK-TERM-EN</sub> | Time for the Clock Lane receiver to enable                  | Time for Dn to             |     | 38      | ns   |

|                          | the HS line termination, starting from the                  | reach V <sub>TERM-EN</sub> |     |         |      |

|                          | time point when Dn crosses V <sub>IL,MAX</sub> .            |                            |     |         |      |

| T <sub>CLK-PREPARE</sub> | Time that the transmitter drives the Clock                  | 38                         |     | 95      | ns   |

|                          | Lane LP-00 Line state immediately before                    |                            |     |         |      |

|                          | the HS-0 Line state starting the HS                         |                            |     |         |      |

|                          | transmission.                                               |                            |     |         |      |

| T <sub>CLK-PRE</sub>     | Time that the HS clock shall be driven by the               | 8                          |     |         | UI   |

|                          | transmitter prior to any associated Data                    |                            |     |         |      |

|                          | Lane beginning the transition from LP to HS                 |                            |     |         |      |

|                          | mode.                                                       |                            |     |         |      |

| T <sub>CLK-PREPARE</sub> | T <sub>CLK-PREPARE</sub> + time that the transmitter drives | 300                        |     |         | ns   |

| + T <sub>CLK-ZERO</sub>  | the HS-0 state prior to starting the Clock.                 |                            |     |         |      |

| T <sub>D-TERM-EN</sub>   | Time for the Data Lane receiver to enable                   | Time for Dn to             |     | 35ns    |      |

|                          | the HS line termination, starting from the                  | reach V <sub>TERM-EN</sub> |     | +4*UI   |      |

|                          | time point when Dn crosses V <sub>IL,MAX</sub> .            |                            |     |         |      |

| T <sub>HS-PREPARE</sub>  | Time that the transmitter drives the Data                   | 40ns + 4*UI                |     | 85 ns + | ns   |

|                          | Lane LP-00 Line state immediately before                    |                            |     | 6*UI    |      |

|                          | the HS-0 Line state starting the HS                         |                            |     |         |      |

|                          | transmission                                                |                            |     |         |      |

| T <sub>HS-PREPARE</sub> | T <sub>HS-PREPARE</sub> + time that the transmitter drives | 145ns + 10*UI |                       |                       | ns |

|-------------------------|------------------------------------------------------------|---------------|-----------------------|-----------------------|----|

| + T <sub>HS-ZERO</sub>  | the HS-0 state prior to transmitting the Sync              |               |                       |                       |    |

|                         | sequence.                                                  |               |                       |                       |    |

| T <sub>HS-TRAIL</sub>   | Time that the transmitter drives the flipped               | 60ns + 4*UI   |                       |                       | ns |

|                         | differential state after last payload data bit of          |               |                       |                       |    |

|                         | a HS transmission burst                                    |               |                       |                       |    |

| T <sub>LPX(M)</sub>     | Transmitted length of any Low-Power state                  | 50            |                       | 150                   | ns |

|                         | period of MCU to display module                            |               |                       |                       |    |

| T <sub>TA-SURE(M)</sub> | Time that the display module waits after the               | $T_{LPX(M)}$  |                       | 2*T <sub>LPX(M)</sub> | ns |

| , ,                     | LP-10 state before transmitting the Bridge                 | , ,           |                       |                       |    |

|                         | state (LP-00) during a Link Turnaround.                    |               |                       |                       |    |

| $T_{LPX(D)}$            | Transmitted length of any Low-Power state                  | 50            |                       | 150                   | ns |

|                         | period of display module to MCU                            |               |                       |                       |    |

| T <sub>TA-GET(D)</sub>  | Time that the display module drives the                    |               | 5*T <sub>LPX(D)</sub> |                       | ns |

|                         | Bridge state (LP-00) after accepting control               |               |                       |                       |    |

|                         | during a Link Turnaround.                                  |               |                       |                       |    |

| $T_{TA-GO(D)}$          | Time that the display module drives the                    |               | 4*T <sub>LPX(D)</sub> |                       | ns |

| , ,                     | Bridge state (LP-00) before releasing control              |               |                       |                       |    |

|                         | during a Link Turnaround.                                  |               |                       |                       |    |

| T <sub>TA-SURE(D)</sub> | Time that the MPU waits after the LP-10                    | $T_{LPX(D)}$  |                       | 2*T <sub>LPX(D)</sub> | ns |

|                         | state before transmitting the Bridge state                 | <b>&gt;</b>   |                       |                       |    |

|                         | (LP-00) during a Link Turnaround.                          |               |                       |                       |    |

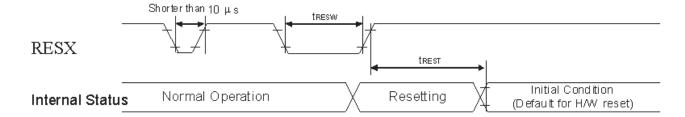

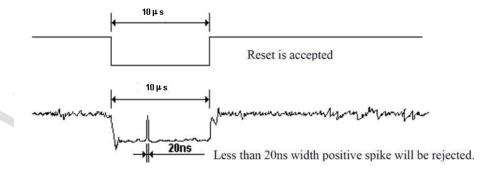

## 4. Display RESET Timing Characteristics

#### Reset input timing

IOVCC=1.65 to 1.95V, VCI=2.8 to 3.2V, GND=0V, Ta=-20 to  $70^{\circ}$ C

#### **Timing Parameters**

| Symbol            | Parameter                 | Related<br>Pins | MIN | ТҮР | MAX | Note                                     | Unit |

|-------------------|---------------------------|-----------------|-----|-----|-----|------------------------------------------|------|

| t <sub>RESW</sub> | *1) Reset low pulse width | RESX            | 10  | -   | -   | -                                        | μs   |

|                   |                           | -               | -   | -   | 5   | When reset applied during Sleep in mode  | ms   |

| t <sub>REST</sub> | *2) Reset complete time   | -               |     | -   | 120 | When reset applied during Sleep out mode | ms   |

Note 1. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below.

| RESX Pulse           | Action                         |  |  |

|----------------------|--------------------------------|--|--|

| Shorter than 5µs     | Invalid Reset                  |  |  |

| Longer than 10μs     | Valid Reset                    |  |  |

| Between 5μs and 10μs | Reset Initialization Procedure |  |  |

- Note 2. During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In –mode) and then return to Default condition for H/W reset.

- Note 3. During Reset Complete Time, data in OTP will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time (tREST) within 5ms after a rising edge of RESX.

- Note 4. Spike Rejection also applies during a valid reset pulse as shown below:

Note 5. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

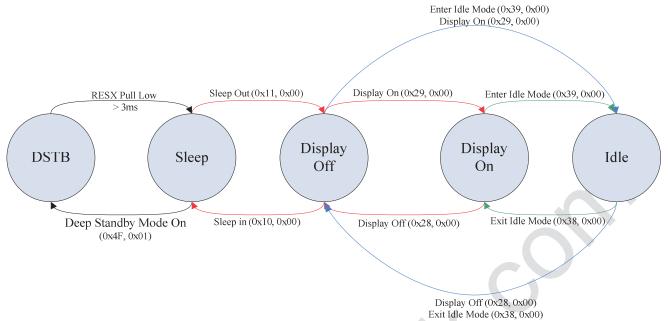

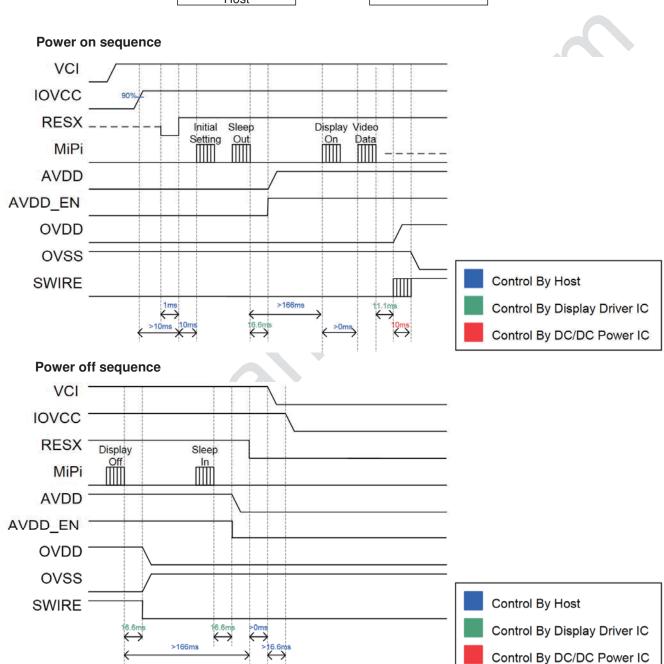

## 5. Recommended Operating Sequence

#### State Diagram

#### **Power Structure**

Please follow AUO's main FPC design suggestion.

Timing settings of Green are controlled by display driver IC. (The settings couldn't be adjusted.) Timing settings of Red are controlled by DC/DC power IC. (The settings couldn't be adjusted.)

## Initial Setting:

| Item | Parameter Quantity                   |  | P0 |  |  |

|------|--------------------------------------|--|----|--|--|

|      | Reference H381DLN01 Application Note |  |    |  |  |

## Sleep Out:

| Item | Parameter Quantity | Address | P0   |

|------|--------------------|---------|------|

| 1    | 1                  | 0x11    | 0x00 |

## Display On:

| Item | Item Parameter Quantity Address |      | P0   |

|------|---------------------------------|------|------|

| 1    | 1                               | 0x29 | 0x00 |

### Sleep In

| Item | em Parameter Quantity Address |      | P0   |

|------|-------------------------------|------|------|

| 1    | 1                             | 0x10 | 0x00 |

## Display Off:

| Item | Parameter Quantity | Address | P0   |

|------|--------------------|---------|------|

| 1    | 1                  | 0x28    | 0x00 |

## D. Optical Specification

All optical specifications are measured under typical condition. (Note 1)

| Item                  |         | Abbr.                     | Min.  | Тур.  | Max.  | Unit | Remark        |

|-----------------------|---------|---------------------------|-------|-------|-------|------|---------------|

| Brightness            |         | Y @ θ=0°                  | 80    | 100   |       | nits |               |

|                       |         | @ θ=0°                    | 3000  |       |       |      |               |

| Contrast ra           | atio    | @ θ=60°                   | 900   |       |       |      |               |

|                       |         | @ θ=80°                   | 480   |       |       |      | Note 0        |

|                       |         | Тор                       | 80    |       |       | Deg. | Note 2        |

| Viewing ar            | ngle    | Bottom                    | 80    |       |       | Deg. |               |

| (CR > 48              | 0)      | Left                      | 80    |       |       | Deg. |               |

|                       |         | Right                     | 80    |       |       | Deg. |               |

|                       | Dod     | х                         | 0.640 | 0.670 | 0.700 |      |               |

|                       | Red     | у                         | 0.300 | 0.330 | 0.360 |      |               |

|                       | Green   | Х                         | 0.186 | 0.236 | 0.286 |      |               |

| Chromaticity          |         | У                         | 0.661 | 0.711 | 0.761 |      | Note 3        |

| (CIE1931)             | Blue    | Х                         | 0.090 | 0.130 | 0.170 |      | Note 3        |

|                       | blue    | у                         | 0.025 | 0.065 | 0.105 |      |               |

|                       | White   | х                         | 0.28  | 0.30  | 0.32  |      |               |

|                       | vvriite | у                         | 0.29  | 0.31  | 0.33  |      |               |

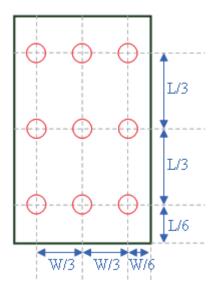

| Uniformi              | ty      | 9 points                  | 70    |       |       | %    | Note 4        |

| Flicker               |         |                           |       |       | -30   | dB   | Note 5        |

| Crosstalk             |         |                           |       |       | 4.0   | %    | Note 6        |

| Life Tim              | е       | 95% @ 25°C                | 100   |       |       | hrs  | Note 7        |

| Response <sup>-</sup> | Гime    | 25°C<br>Between 10% & 90% |       |       | 2     | ms   | For Reference |

Please follow AUO's main FPC design suggestion.

If you don't follow the AUO's main FPC design suggestion, then optical performance is not guaranteed.

## Note 1: Typical Condition

Optical characteristics should be measured at the **center area** of the display with **Konica Minolta CA-310** and at the ambient temperature = 25°C ±2°C and in the dark room.

### Note 2: Viewing Angle & Contrast Ratio

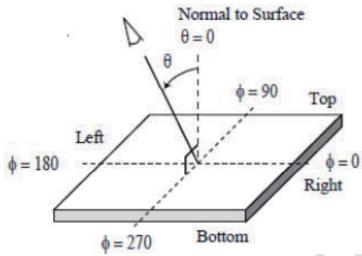

The optical performance is specified as the driver IC located at  $\phi = 270^{\circ}$ .

Contrast ratio is calculated with the following formula:

Contrast ratio (**CR**) = Photo detector output when OLED is at "**White**" pattern

Photo detector output when OLED is at "**Black**"

## Note 3: Chromaticity

Chromaticity of **R**, **G**, **B** pattern are measured at Gray Level "255". Chromaticity of **White** pattern are measured at Gray Level "255".

## Note 4: Uniformity

Global LCD Panel Exchange Center

Uniformity under White (L255) pattern =

## minimum luminance of 9 maximum luminance of 9

#### Note 5: Flicker

Suggested Instruments: Konica Minolta CA-310

Measuring Point: Center point of 128th gray

The flicker level is defined using Fast Fourier Transformation (FTT) as follows:

Flic ker =

$$20 \log_{10} \left( 2 \frac{f_{FFTC}(n)}{f_{FFTC}(0)} \right) + FS(Hz)$$

(dB)

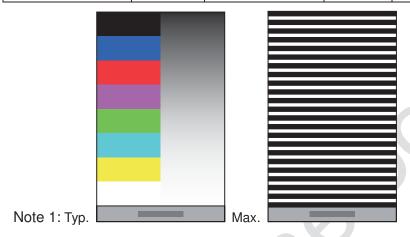

where fFFTC(n) is the nth FFT coefficient, and fFFTC(0) is the 0th FFT coefficient which is DC component. FS (Hz) is the flicker sensitivity as a function of frequency. The flicker level shall be measured with the test pattern in below.

Test Pattern: L128 Gray

#### Note 6: Crosstalk

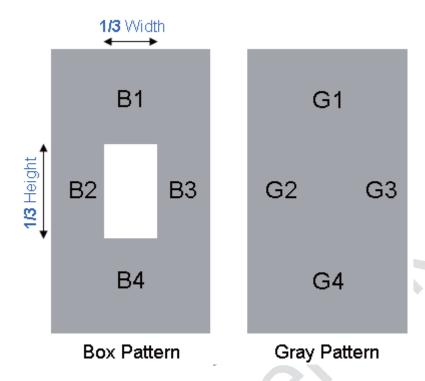

Crosstalk shall be calculated by the luminance of **B1~B4** and **G1~G4** in the patterns shown below.

Box Pattern: **L128** gray level background with a **L255** White window in the central area.

Gray Pattern: L128 gray level background only.

Crosstalk

$$\equiv Maximum: \left\{ \frac{|B1 - G1|}{G1}, \frac{|B2 - G2|}{G2}, \frac{|B3 - G3|}{G3}, \frac{|B4 - G4|}{G4} \right\} \times 100\%$$

#### Note 7: Life Time

OLED life time is defined by the **Minimum Duration Time** that the luminance is decayed to a specific ratio (ex. **95%**) of initial state.

Test Pattern under duration period: L255 White

E. Reliability Test Items

In the standard condition, there should **not** be any display function NG issue occurred during the reliability test and the performance is confirmed after panel is left at room temperature. All the cosmetic specifications are judged only **before** the reliability stress.

| No. | Test items                            | Conditions                                                             |        | Remark        |

|-----|---------------------------------------|------------------------------------------------------------------------|--------|---------------|

| 1   | High Temperature Storage              | T= 80°C                                                                | 100Hrs |               |

| 2   | Low Temperature Storage               | T= -40°C                                                               | 100Hrs |               |

| 3   | High Temperature Operation            | T= 70°C                                                                | 100Hrs | Note 1        |

| 4   | Low Temperature Operation             | T= -20°C                                                               | 100Hrs |               |

| 5   | High Temperature & Humidity Operation | T= 60°C . 90% RH                                                       | 100Hrs |               |

| 6   | Thermal Shock                         | -30°C ~ 80°C, 30 cycle, 1Hrs/cycle                                     |        | Non-operation |

| 7   | Electrostatic Discharge               | Contact = ± 4 kV, Class B Air = ± 8 kV, Class B                        |        | Note 2        |

| 8   | Vibration (With Carton)               | 1.5Grms, 10~200Hz<br>Total time: 90 mins<br>(30 mins/axis for X, Y, Z) |        |               |

| 9   | Drop (With Carton)                    | Height: 60cm<br>1 corner, 3 edges, 6 surfaces                          |        |               |

Note 1: T = Ambient Temperature

Please follow AUO's main FPC design suggestion.

If you don't follow the AUO's main FPC design suggestion, then reliability items are not guaranteed.

Note 2: All test techniques follow IEC 61000-4-2 standard.

| Test Condition           |                                                                                                                                                |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pattern                  |                                                                                                                                                |  |

| Procedure<br>&<br>Set-up | Contact Discharge : 330 $\Omega$ , 150pF, 1sec, 5 point, 10 times/point<br>Air Discharge : 330 $\Omega$ , 150pF, 1sec, 5 point, 10 times/point |  |

|          | Emz                   |  |

|----------|-----------------------------------------------------------|--|

| Criteria | Class B – Some performance degradation allowed.           |  |

| Ontona   | No data lost. Self-recoverable hardware failure.          |  |

| Othore   | 1. Air Discharge: Gun to Panel Distance>1cm               |  |

| Others   | 2. No MiPi D-PHY command, keep default register settings. |  |

## F. Precautions

- 1. Do not twist or bend the module and prevent the unsuitable external force for display module during assembly.

- 2. Adopt measures for good heat radiation. Be sure to use the module within the specified temperature.

- 3. Avoid dust or oil mist during assembly.

- 4. Follow the correct power sequence while operating. Do not apply the invalid signal, otherwise, it will cause improper shut down and damage the module.

- 5. Less EMI: it will be more safety and less noise.

- 6. Please operate module in suitable temperature. The response time & brightness will drift by different temperature.

- 7. Avoid to display the fixed pattern (exclude the white pattern) in a long period; otherwise, it will cause image sticking.

- 8. Be sure to turn off the power when connecting or disconnecting the circuit.

- 9. Display surface never likes dirt or stains.

- 10. A dewdrop may lead to destruction. Please wipe off any moisture before using module.

- 11. Sudden temperature changes cause condensation, and it will cause polarizer damaged.

- 12. High temperature and humidity may degrade performance. Please do not expose the module to the direct sunlight and so on.

- 13. Acetic acid or chlorine compounds are not friends with TFT display module.

- 14. Static electricity will damage the module; please do not touch the module without any grounded device.

- 15. Do not disassemble and reassemble the module by self.

- 16. Be careful do not touch the rear side directly.

- 17. No strong vibration or shock. It will cause module broken.

- 18. Storage the modules in suitable environment with regular packing.

- 19. Be careful of injury from a broken display module.

- 20. Please avoid the pressure adding to the surface (front or rear side) of modules, because it will cause the display non-uniformity or other function issue.

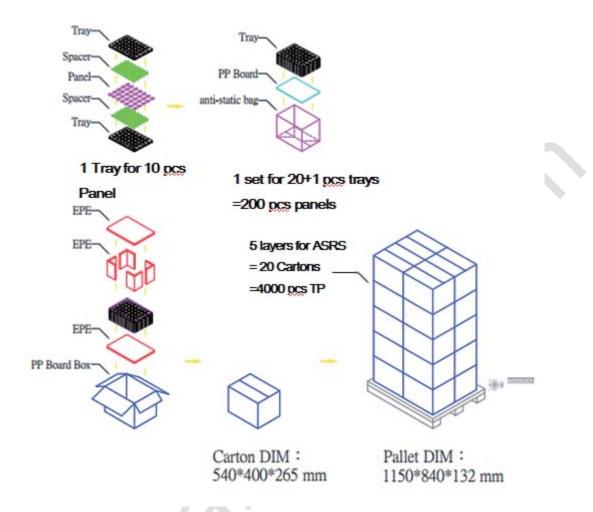

## **G. Packing Information**

#### **Packing Form**

H. Outline Dimension

ALL RIGHTS STRICTLY RESERVED. ANY PORTION OF THIS PAPER SHALL NOT BE REPRODUCED, COPIED, OR TRANSFORMED TO ANY OTHER FORMS WITHOUT PERMISSION FROM AU OPTRONICS CORP.